# EGC442 Class Notes 3/31/2023

Baback Izadi Division of Engineering Programs bai@engr.newpaltz.edu

How many stages exist in the laundry analogy?

| +      |  |

|--------|--|

|        |  |

|        |  |

| Ohaala |  |

k Show answer

2) If laundry is done sequentially, how many minutes do 60 loads take to wash, dry, fold, and put away?

Check

Show answer

3) If laundry is done in a pipelined manner, execution is nearly 4 times faster than if done sequentially. Suppose doing 50 loads sequentially requires 6000 minutes. How long would those 50 loads take if done in a pipelined manner? Assume a 4 times speedup (ignore the fact that some stages are unused for the first few and last few loads).

1500 minutes

Show answer

4) Each load of laundry takes 4 × 30 = 120 minutes to wash, dry, fold, and store (30 minutes each). How many minutes are required to complete one load of laundry when multiple loads of laundry are done in a pipelined manner?

| 120 |  |   |

|-----|--|---|

|     |  | _ |

Check

minutes

Check Show answer

# Correct

# 4

The four stages are washing, drying, folding, and storing. Each stage is assumed to require 30 minutes.

# Correct

# 7200

One load takes 30 × 4 or 120 minutes, so 60 loads takes 60 × 120 = 7200 minutes. Seems like a shame that the washing machine isn't being used at the same time as the dryer though, right?

# Correct

6000 / 4 = 1500. If pipelining stages are equal in length and the stages can be kept busy, speedup can approach the number of stages, making pipelining very attractive.

#### Correct

# 120

Pipelining doesn't affect the time to do one particular load. Each stage still takes 30 minutes, so one load takes  $4 \times 30 = 120$  minutes to wash, dry, fold, and store. What pipelining does is start washing a second load while the first load is drying, and start washing a third load while the second load is drying and the first is being folded, and so on. So multiple loads are being processed at the same time. The nonpipelined datapath implementation has how many stages?

1

0 5

2) The pipelined datapath implementation has how many stages?

O 1

5

7) The above figure shows the five stages as: Instruction fetch, Reg, ALU, Data access, and Reg. Are the two Regs doing the same thing?

- O Yes

- 🖲 No

Does every instruction require all 5 stages?

- O Yes

- 🖲 No

Suppose Instr1 is fetched in stage 1. Instr1 then proceeds to stage 2, Reg read. In a pipelined implementation, can Instruction2 be fetched simultaneously with that Reg read?

- 🔘 Yes

- O No

#### Correct

The implementation has just one long stage. Such a stage is akin to a single laundry person doing laundry by hand, who first washes, then blow dries, then folds, and finally stores each load sequentially.

#### Correct

The one long stage has been divided into 5 shorter stages: Instr fetch, Reg read, ALU op, Data access, and Reg write. Such division is akin to replacing one laundryby-hand person with four people/machines: a washer, dryer, folder, and storer.

## Correct

No, the first Reg represents the register read stage, while the second Reg represents the register write stage. The two just happen to use the same abbreviated word Reg.

$\checkmark$

# Correct

beq, for example, only requires the first three stages. However, for simplicity, every instruction will take 5 stages long.

#### Correct

Indeed, such overlapping execution is the main point of pipelining.

On computer X, a nonpipelined instruction execution would require 12 ns, and thus 12 ns exists between instructions. A pipelined implementation uses 6 equal-length stages of 2 ns each, resulting in \_\_\_\_\_ns between instructions.

- $O_1$

- 2

7) On computer X, a nonpipelined instruction execution would require 12 ns. A pipelined implementation uses 6 equal-length stages of 2 ns each. Assuming one million instructions execute and ignoring empty stages at the start/end, what is the speedup of the pipelined vs. nonpipelined implementation?

O 2 6

After 2 ns. a first instruction Instr1 would be done with stage 1, meaning Instr2 could begin stage 1.1 ns is too short: Instr1 would only be halfway through stage 1 before Instr2 tried to use stage 1, resulting in a problem. The general equation is 12 ns / 6 stages = 2 ns between instructions.

$\checkmark$

### Correct

Non-pipelined time: 1,000,000 \* 12 ns = 12,000,000 ns. Pipelined time: 1,000,000 \* 2 ns = 2,000,000 (each instruction starts 2 ns after the previous, so each adds 2 ns). 12.000.000 ns / 2.000.000 ns = 6.

Under ideal conditions the speed-up from pipelining is approximately equal to the number of pipe stages.

12) Match the pipeline stage with the physical resource whose icon represents that stage in the stylized datapath depictions. • IM • Reg (write) • DM • ALU • Reg (read) Stage 1: IF (instruction fetch) TMStage 2: ID (instruction decode) Reg (Vead) Stage 3: EX (execute) ALU Stage 4: MEM (data memory access) DM Stage 5: WB (write back) Reg (write)

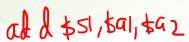

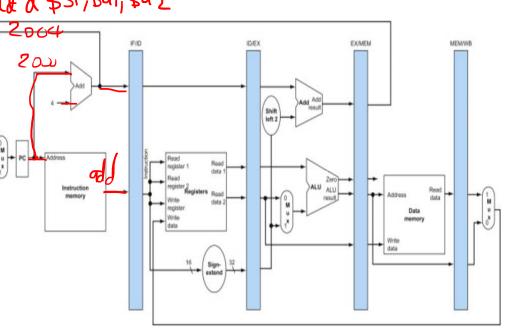

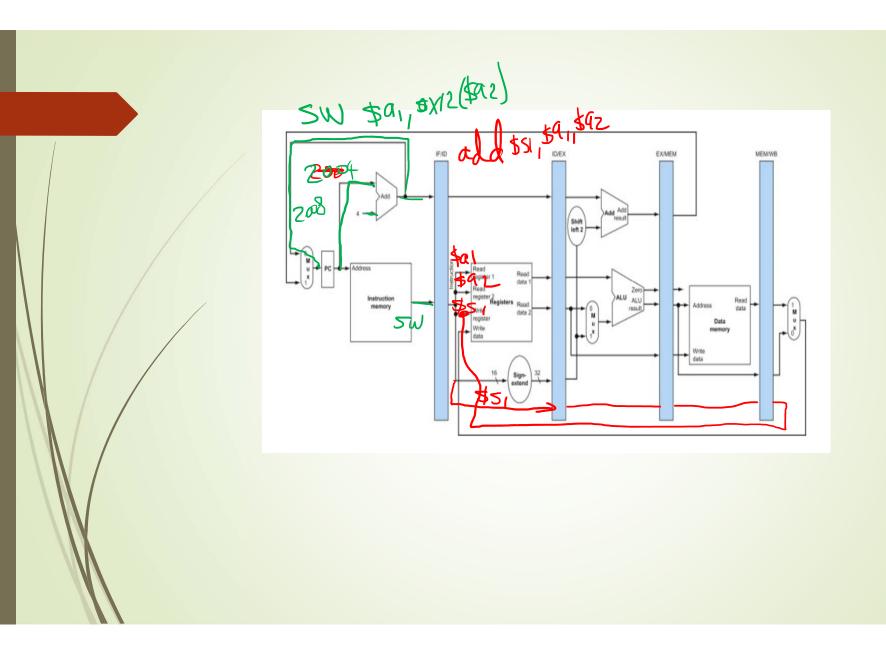

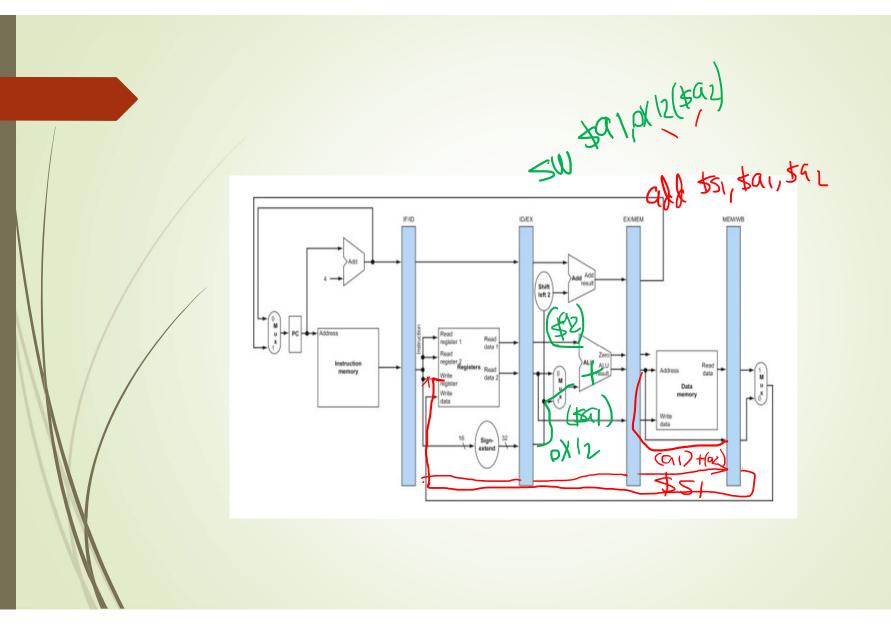

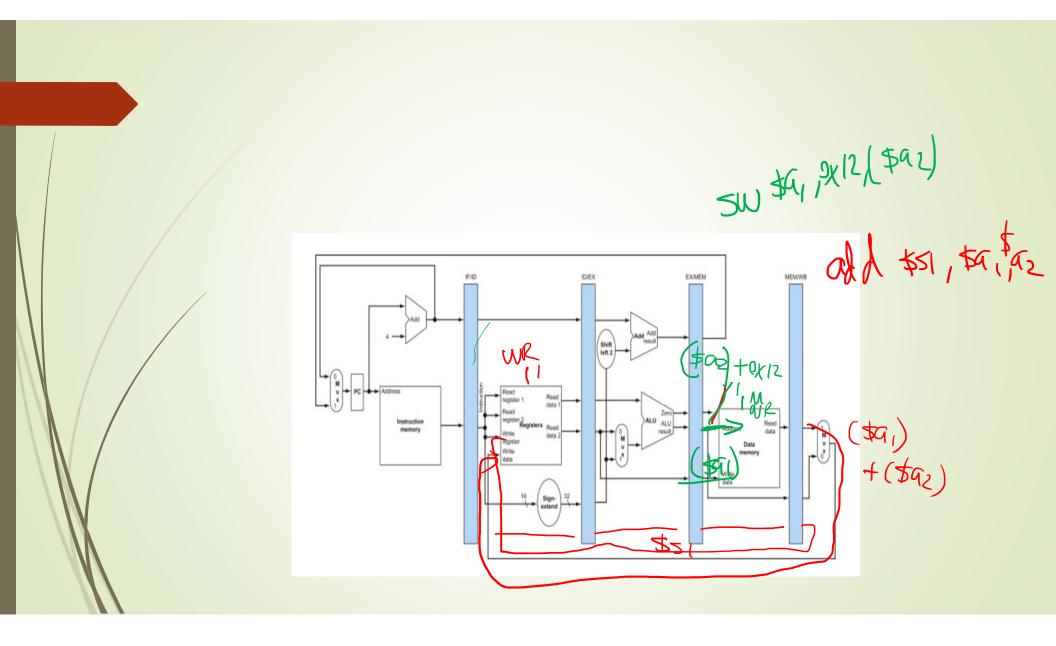

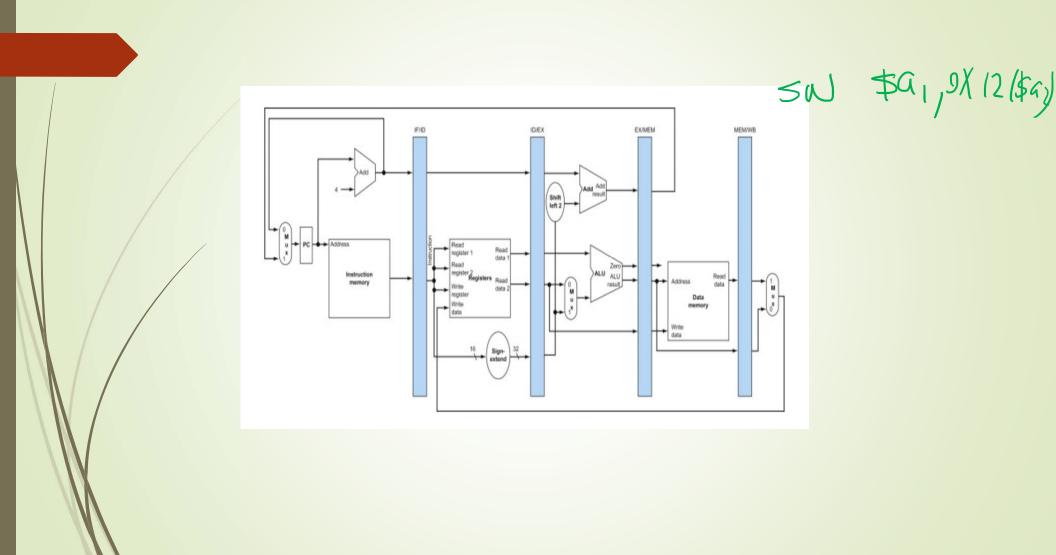

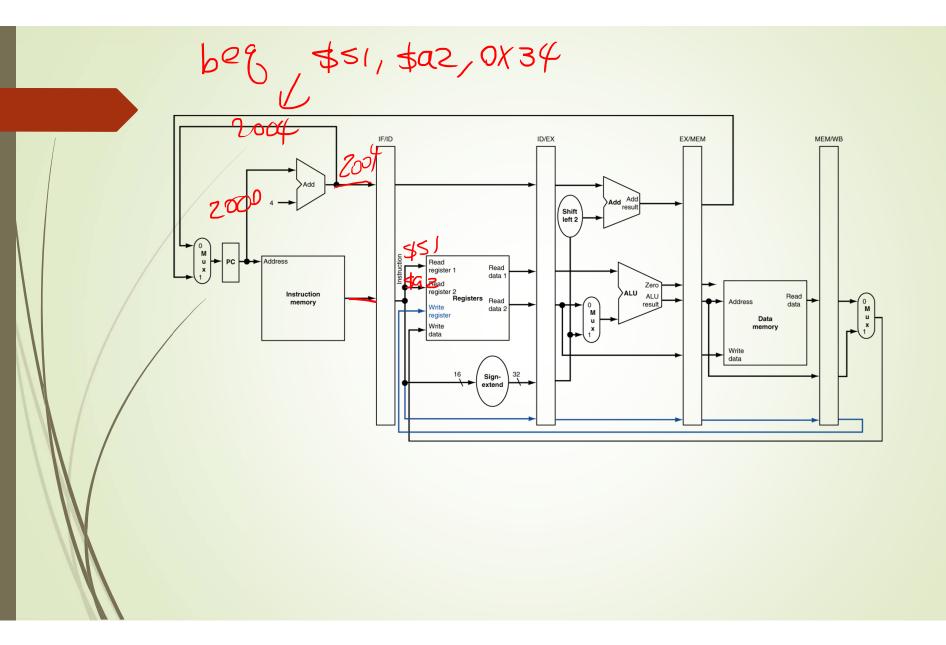

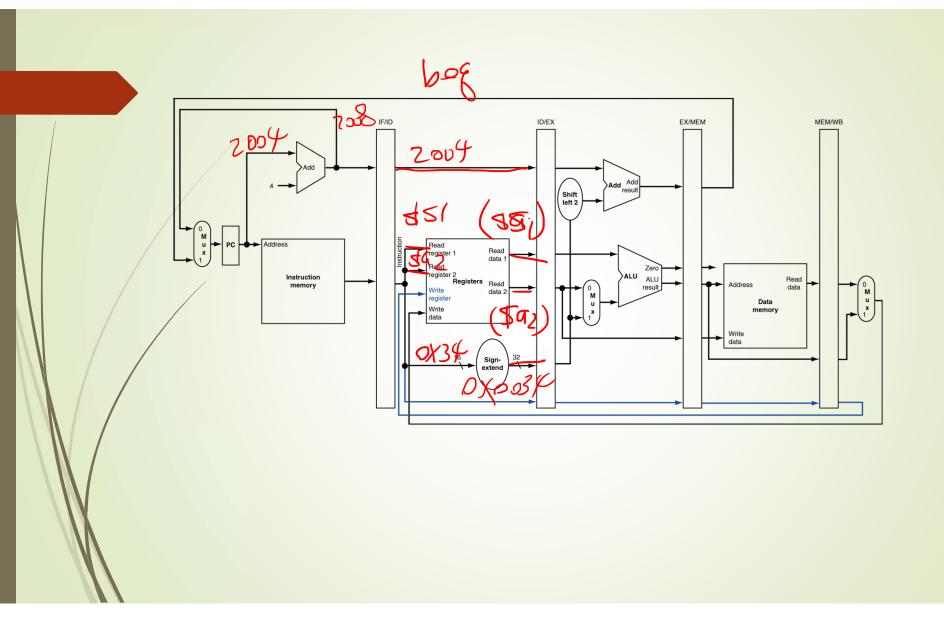

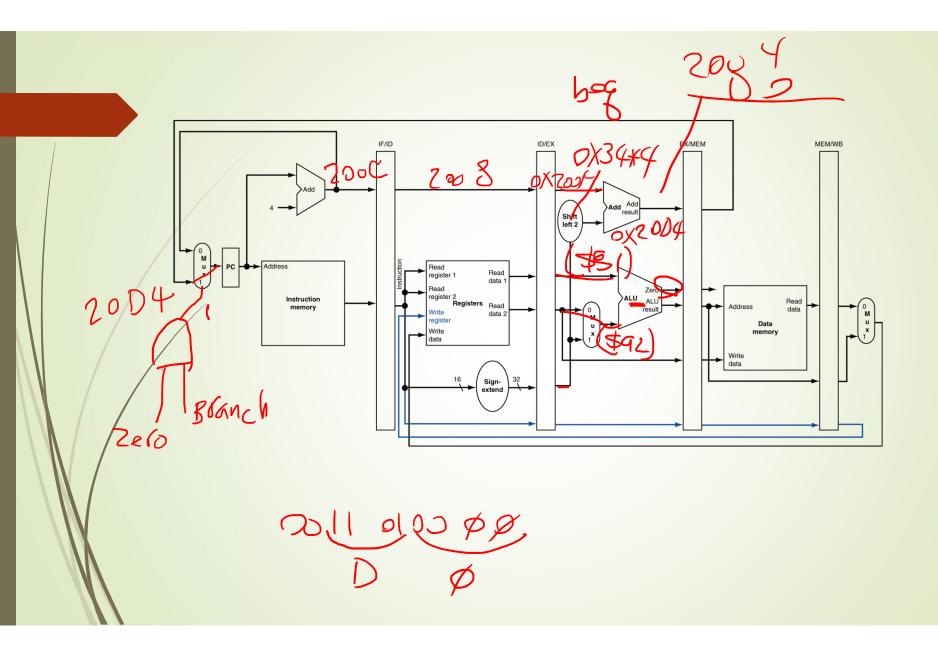

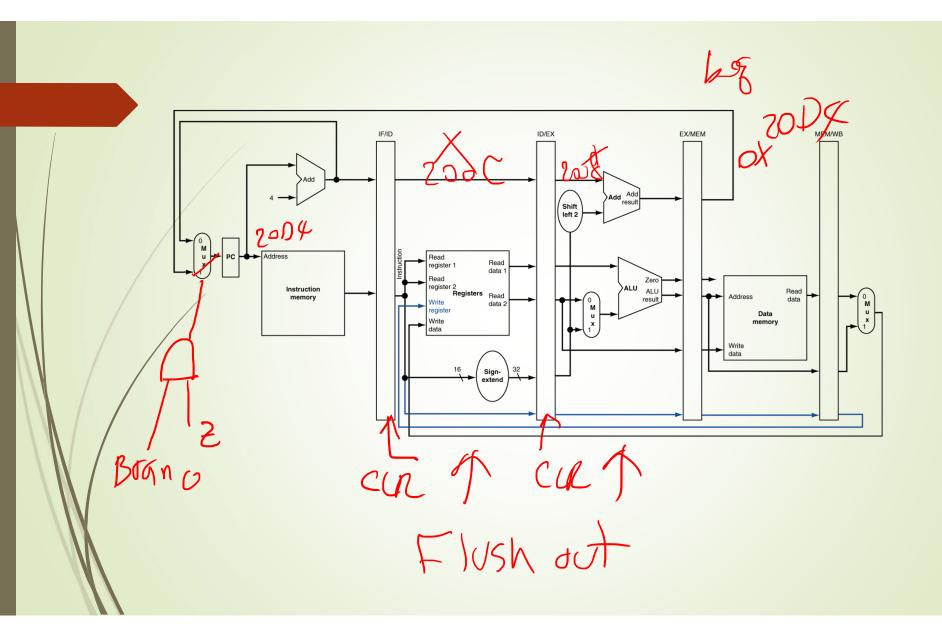

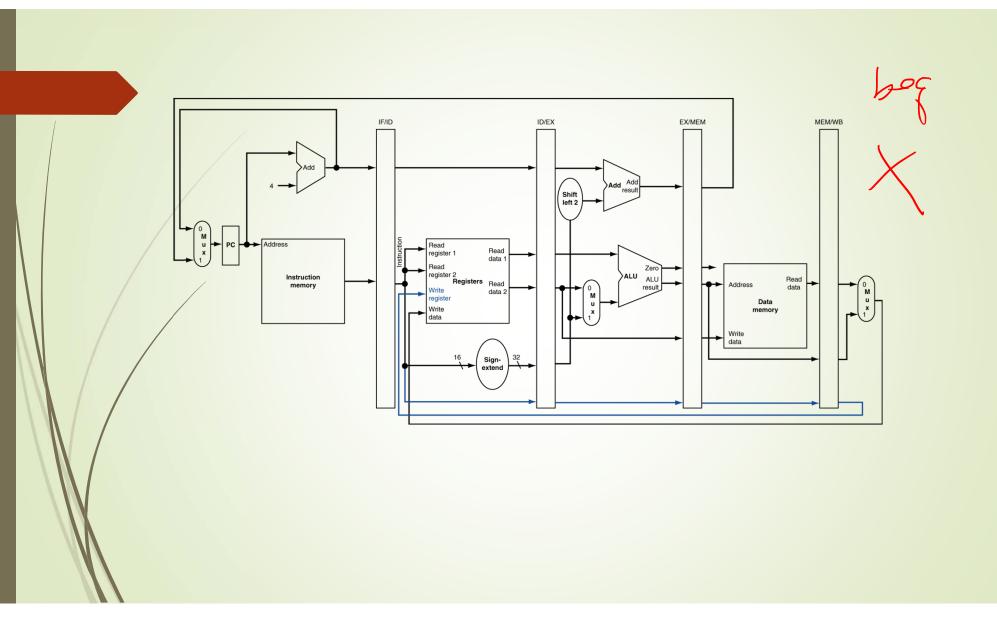

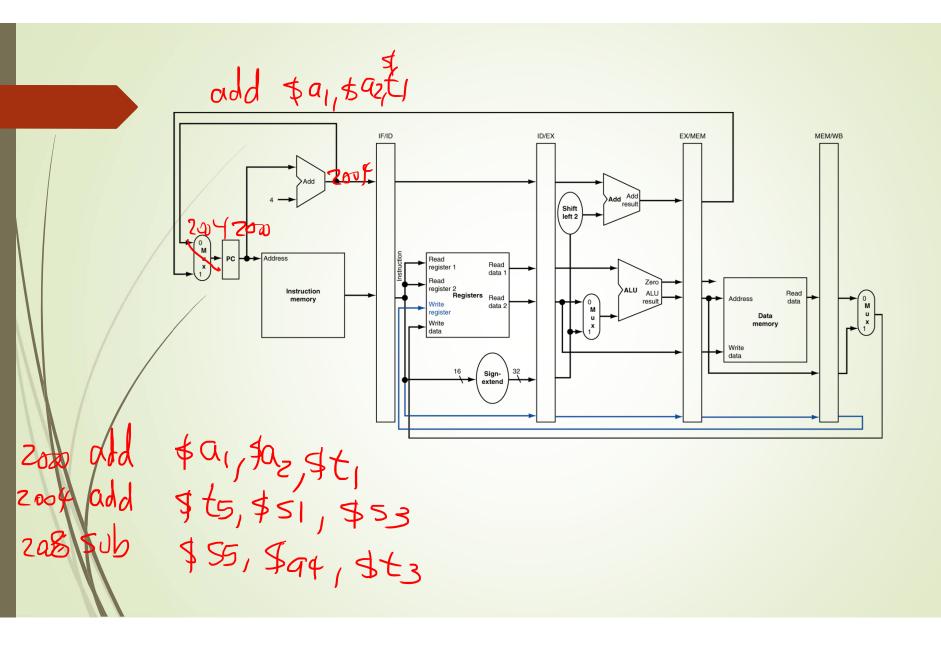

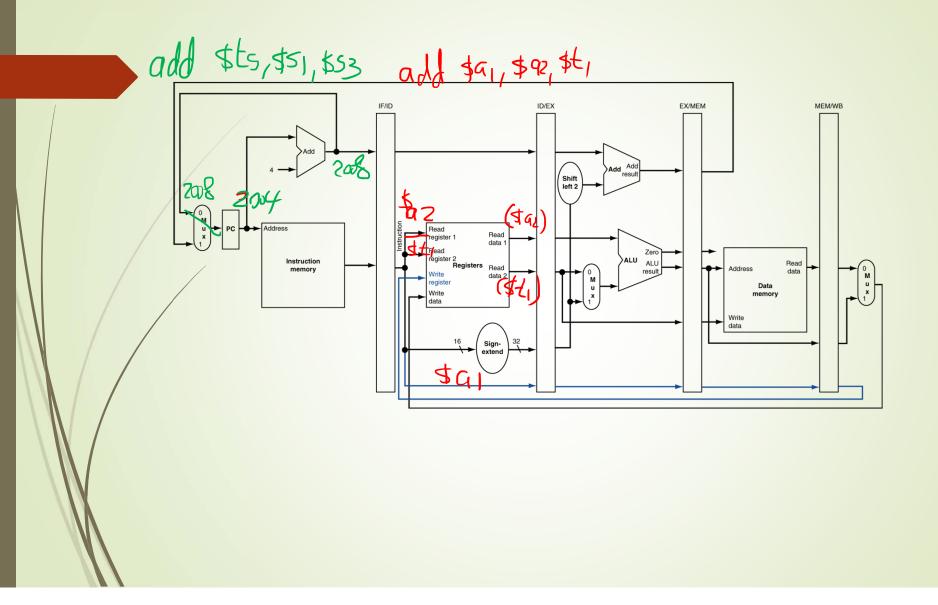

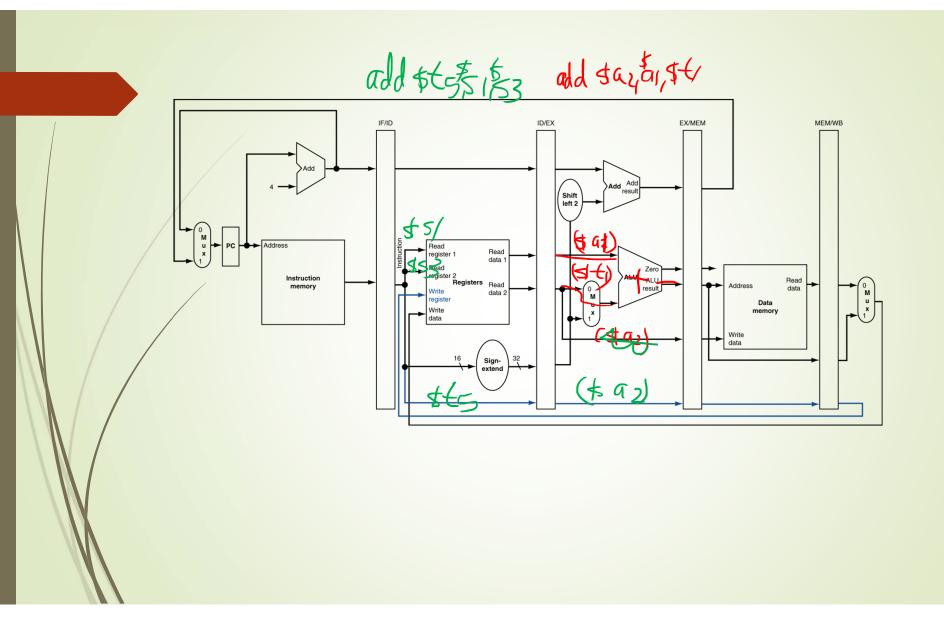

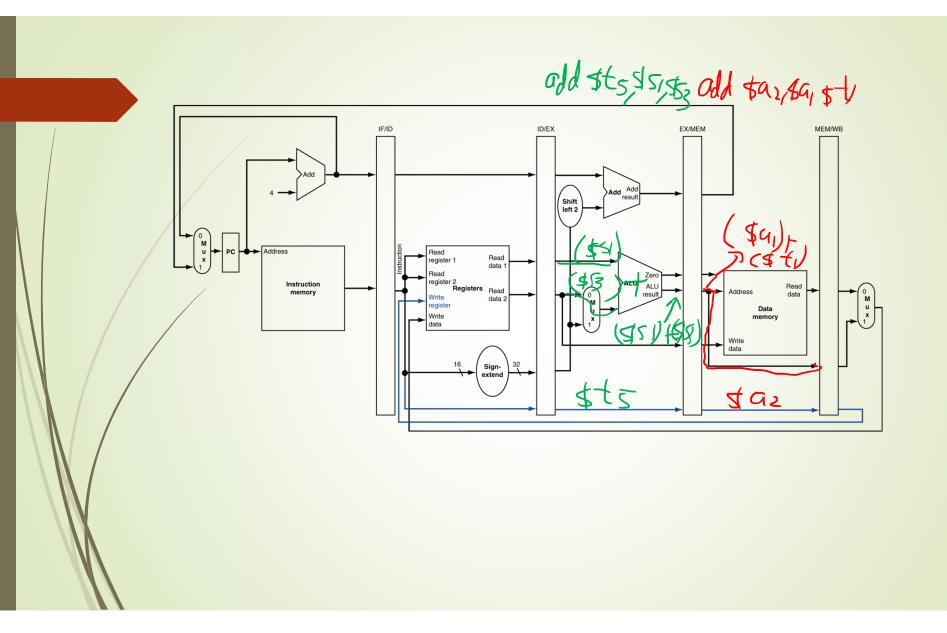

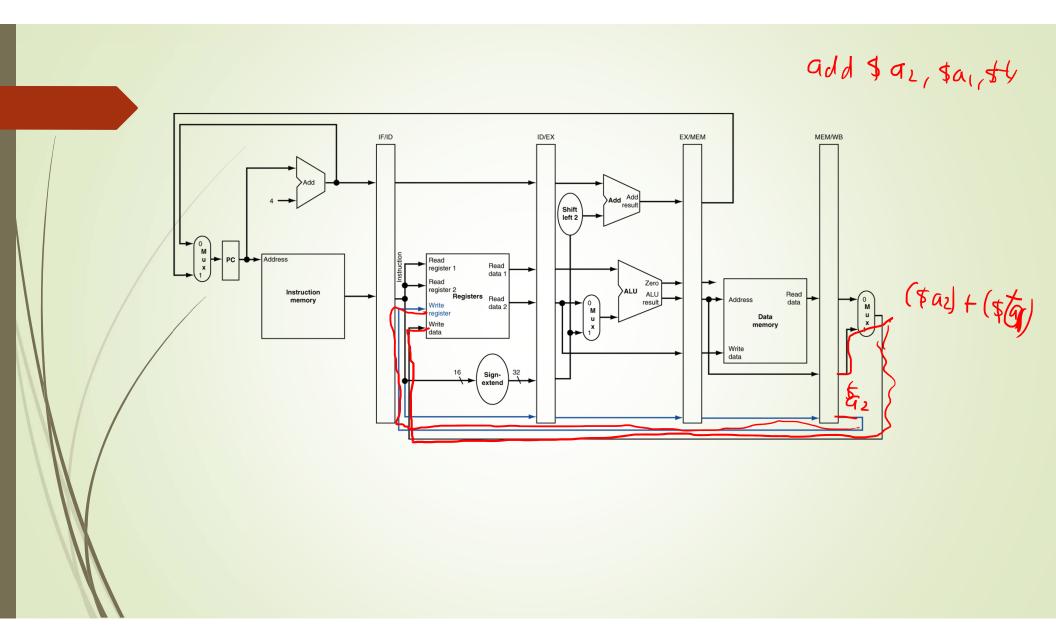

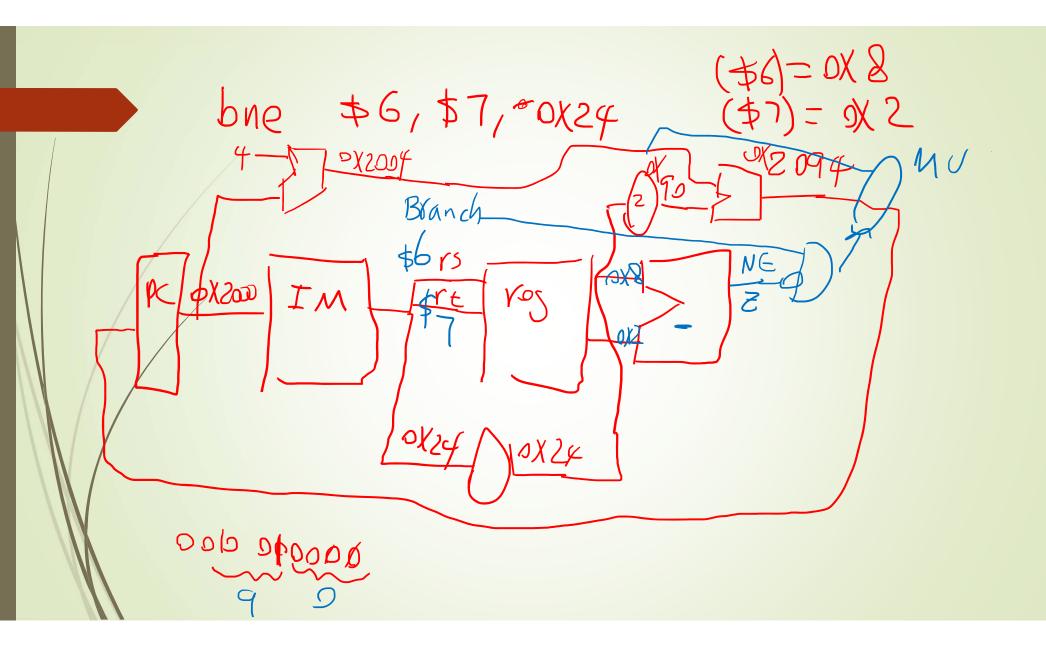

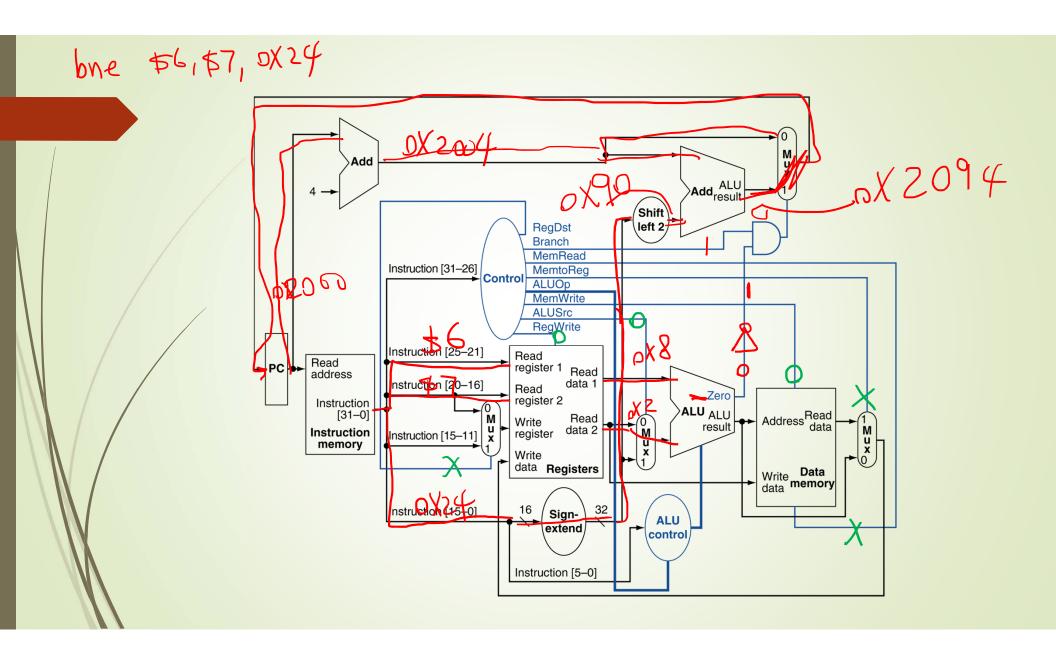

13) Using multiple copies of the following diagram, show the active stages for execution of the following sequence of instruction set

2000 2004 add \$s1, \$a1, \$a2 sw \$a1, 0x12 (\$a2)